|

| Home | Stephan Linz | Projekte | Hobby | Kontakt | Nutzerzugang |

| Home Hobby Elektronika PC Mugler Erweiterungen Floppy-Disk-Interface |

|

Stephan Linz |

|||||

|

Projekte |

|||||

|

Hobby |

|||||

|

Elektronika |

|||||

|

PC Mugler |

|||||

|

Allgemeines |

|||||

|

Grundsystem |

|||||

|

Erweiterungen |

|||||

|

AV RISC |

|||||

|

DIA Vision |

|||||

|

Systematika |

|||||

|

Modellbahn |

|||||

|

Wandern |

|||||

|

Kontakt |

|||||

|

Nutzerzugang |

|||||

Floppy-Disk-Interface

- FA-102/1990 S.63-66, 3.US

- FA-9/1990 S.441

Floppy-Disk-Interface für den PC/M

2 Funktionsbeschreibung

3 Inbetriebnahme

4 Anschluss von 8-Zoll Laufwerken

5 Software

6 FDC-PLL-Abgleich

7 Zusätze und Erfahrungen

7.2 Änderungen

7.3 Stückliste

Literatur

| [1] | "Beschreibung K 5120 - Ansteuerung Magnetfolienspeicher" VEB Kombinat Robotron |

| [2] | E. Böhl: "Anwendungen des FDC U 8272 D" Mikroprozessortechnik 3 (1989), H.2, S.39-41 ISSN: 0233-2892; ThULB Jena: 4 Z 2644 :34.1985 (Magazin) |

| [3] | E Kühne: "Floppy-Disk-Laufwerk am A 5120" radio fernsehen elektronik 38 (1989), H.4, S.219-221 ISSN: 0033-7900 - 1436-1574; ThULB Jena: 4 Z 401 (Magazin) |

| [4] | "Betriebsdokumentation - Diskettenspeicher MFS 1.6 (TEAC) K5601" VEB Kombinat Robotron |

| [5] | "Technologische Unterlagen des Floppymodul am Z9001 bzw. KC85/1" VEB Kombinat Robotron (dig. Aufbereitung: Hr. U. Zander; Vielen Dank) Schaltplan Z9001 Floppymodul Leiterplatte Z9001 Floppymodul Bestückungsplan Z9001 Floppymodul Prüfplan Z9001 Floppymodul |

| [6] | "Technologische Unterlagen des Floppymodul am A 5105 bzw. BIC" VEB Kombinat Robotron (dig. Aufbereitung: Hr. U. Zander; Vielen Dank) Schaltplan A 5105 Floppymodul Leiterplatte A 5105 Floppymodul (Link defekt, da in Bearbeitung) Bestückungsplan A 5105 Floppymodul |

| [7] | M. Haardt, A. Knaff, D. C. Niemi: "The floppy user guide" englisches Dokument über Aufbau und Funktionsweise von Floppy Disk Laufwerken June 11th, 2001: [PS] [PDF] |

1 Überblick

K 5600.10 (MFS 1.2), 40 Spuren, einseitig, MFM

K 5600.20 (MFS 1.4), 80 Spuren, einseitig, MFM

K 5601 (MFS 1.6), 80 Spuren, doppelseitig, MFM (u.a. auch FD55FV-3-U, FD55FV-03-U, FD55FV-13-U) [4]

Laufwerke mit Shugart-Bus, 40 Spuren, zweiseitig, MFM (Standardlaufwerke in XT-kompatiblen Computern)

| PC/M FD-Steuerung |

K 5600.10 (MFS 1.2) |

K 5600.20 (Shugart-Bus) |

|||||||||||

| A1 | GND | A1 | GND | 2 | n.b. | ||||||||

| A2 | /FLT | A2 | +5V | 4 | /HL | ||||||||

| A3 | /IX | A3 | /MO | 6 | /SE3 | ||||||||

| A4 | /SE2 | A4 | /RDY | 8 | /IX | ||||||||

| A5 | /LCK1 | A5 | /TRO | 10 | /SE0 | ||||||||

| A6 | /FR-/HS | A6 | /WP | 12 | /SE1 | ||||||||

| A7 | /STP | A7 | /FR | 14 | /SE2 | ||||||||

| A8 | /LCT | A8 | /RD | 16 | /LCK | ||||||||

| A9 | /LCK3 | A9 | /IX | 18 | /SD | ||||||||

| A10 | n.b. | A10 | /FLT | 20 | /STP | ||||||||

| A11 | /WE | A11 | GND | 22 | /WD | ||||||||

| A12 | GND | A12 | GND | 24 | /WE | ||||||||

| A13 | GND | A13 | GND | 26 | /TRO | ||||||||

| B1 | GND | B1 | GND | 28 | /WP | ||||||||

| B2 | /HL | B2 | +5V | 30 | /RD | ||||||||

| B3 | /LCK0 | B3 | +5V | 32 | /HS | ||||||||

| B4 | /SE3 | B4 | /HL | 34 | /RDY | ||||||||

| B5 | /RDY | B5 | /SE | Alle ungeraden Kontakte auf GND! Stromversorgung (auf Stecker am Laufwerk gesehen, v.l.n.r):

|

|||||||||

| B6 | /SD | B6 | /STP | ||||||||||

| B7 | /SE1 | B7 | /LCK | ||||||||||

| B8 | /SE0 | B8 | /WD | ||||||||||

| B9 | /LCK2 | B9 | /WE | ||||||||||

| B10 | /WD | B10 | /SD | ||||||||||

| B11 | /TR0 | B11 | +12V | ||||||||||

| B12 | /WP-/TS | B12 | +12V | ||||||||||

| B13 | /RD | B13 | +12V | ||||||||||

| PC/M FD-Steuerung |

K 5600.20 (Lw. B) |

K 5600.10 (Lw. C) |

K 5600.10 (Lw. C) |

|

| A1 | GND | alle unger. | A1, A12, A13, B1 | A1, A12, A13, B1 |

| A2 | /FLT | – | A10 | A10 |

| A3 | /IX | 8 | A9 | A9 |

| A4 | /SE2 | 14 | A3, B4, B5, B7 | – |

| A5 | /LCK1 | 16 | – | – |

| A6 | /FR-/HS | 32 | A10 | A10 |

| A7 | /STP | 20 | B6 | B6 |

| A8 | /LCT | – | – | – |

| A9 | /LCK3 | – | – | – |

| A10 | – | – | – | – |

| A11 | /WE | 24 | B9 | B9 |

| A12 | GND | alle unger. | A1, A12, A13, B1 | A1, A12, A13, B1 |

| A13 | GND | alle unger. | A1, A12, A13, B1 | A1, A12, A13, B1 |

| B1 | GND | alle unger. | A1, A12, A13, B1 | A1, A12, A13, B1 |

| B2 | /HL | 4 | – | – |

| B3 | /LCK0 | – | – | – |

| B4 | /SE3 | 6 | – | A3, B4, B5, B7 |

| B5 | /RDY | 34 | A4 | A4 |

| B6 | /SD | 18 | B10 | B10 |

| B7 | /SE1 | 12 | – | – |

| B8 | /SE0 | 10 | – | – |

| B9 | /LCK2 | – | – | – |

| B10 | /WD | 22 | B8 | B8 |

| B11 | /TR0 | 26 | A5 | A5 |

| B12 | /WP-/TS | 28 | A6 | A6 |

| B13 | /RD | 30 | A8 | A8 |

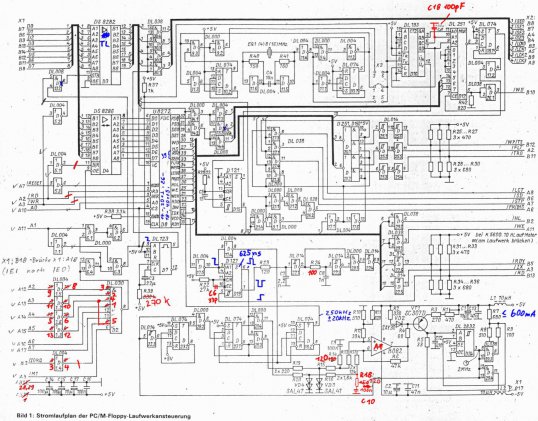

2 Funktionsbeschreibung

Steuerport des FDC: Adresse 0xc0

Datenport des FDC: Adresse 0xc1

Laufwerksauswahl: Adresse 0xc2

Die Aktivierung der Select-Ausgänge (SE0 bis SE3) erfolgt bei jedem Zugriff auf den FDC. Mittels der Port-Dekodierung wird ein nachtriggerbarer Monoflop (D7) angeschlossen. D30 aktiviert daraufhin die Select-Leitungen. Die Einschaltdauer der Floppy-Laufwerke nach dem letzten Zugriff ist durch R39 und C3 auf etwa 4 s festgelegt.

Die Prekompensationssteuerung ist für die 1.2-Laufwerke erforderlich (Kompensation unterschiedlicher Schreibdichte in Abhängigkeit von der Spur). Die Freigabe der Prekompensation erfolgt mit B6 von D3 (DS 8282). Die Realisierung dieser Funktion übernehmen im wesentlichen D16, D12, D17 und D18 (siehe auch [1], [2]). Die Umschaltung des Laufwerktyps ist erforderlich, da verschiedene Laufwerkstypen am selben Bus betrieben werden sollen. Ausgewählt durch B7 von D3 wird entweder das Signal /HS (Kopfauswahl) oder /FR (Fehlerrücksetzen) vom FDC auf den Floppy-Bus (X2) gelegt.

Die Takterzeugung ist so aufgebaut, dass Quarze unterschiedlicher Frequenz zum Einsatz kommen können. Entsprechend sind die Brücken an X3 einzusetzen:

4 MHz Quarz: X3/2 - X3/5

8 MHz Quarz: X3/1 - X3/4

16 MHz Quarz: 3/3 - X3/6

Die Phasenregelschleife (PLL) dient der Synchronisation des vom Floppy-Laufwerk kommenden Datenstroms mit einer Bezugstaktfrequenz. Dazu schwingt ein VCO auf einer Frequenz von 2 MHz (D31, V1, D24). Diese Frequenz wird auf 250 kHz geteilt (D23, D18) und mit der Taktfrequenz der empfangenen Daten synchronisiert. Dadurch erfolgt ein Ausgleich von Abweichungen und Drehzahlschwankungen des Laufwerks. Dies ist besonders beim Austausch von Disketten, die auf anderen Computern aufgezeichnet wurden, von Bedeutung. Die über den Eingang RD empfangenen Daten werden über D19 mit dem Oszillator der PLL synchronisiert und über eine Impulsaufbereitung (D22, D28) an den FDC geliefert [1], [2]. Siehe auch Schaltungsanalyse.

| Ausgang | Bedeutung |

| B1 | SE0 und LCK0 (LW 0 = A, H = Laufwerk aktiv) |

| B2 | SE1 und LCK1 (LW 1 = B, H = Laufwerk aktiv) |

| B3 | SE2 und LCK2 (LW 2 = C, H = Laufwerk aktiv) |

| B4 | SE3 und LCK3 (LW 3 = D, H = Laufwerk aktiv) |

| B5 | z.Z. nicht belegt |

| B6 | Prekompensation (für MFS 1.2, H = Ein) |

| B7 | Umschaltung /FR-/HS-Signal (Typenumschaltung) |

| B8 | TC-Impulseingang am FDC |

3 Inbetriebnahme

Bestückung der Leiterplatte außer FDC nach Bild 4 und Kontrolle auf Kurzschlüsse und Unterbrechungen;

Einbau der Brücke X3 entsprechend dem vorhandenen Quarz;

Anlegen der Betriebsspannung (-5 V für die PLL über den Steckverbinder X1 oder direkt zuführen);

Kontrolle der Taktfrequenz des FDC (4 MHz) an Pin 19 von D8;

Einstellen der Oszillatorfrequenz der PLL mittels R1 und C12 auf 250 kHz an Pin 22 des FDC (DW), (+/- 20 kHz bei 2 MHz am Oszillator), damit wird gleichzeitig die gesamte PLL-Strecke überprüft;

Einsetzen des FDC und Anschließen des Laufwerks entsprechend dem jeweiligen Typ und der Laufwerksnummer (0, 1, 2, 3), siehe Tabelle 1

Nun benötigt man das für diese FD-Steuerung erarbeitete Betriebssystem (Austausch der EPROMs der Systemleiterplatte oder von Kassette nachladbare Version). Nach dessen Start wird das Laufwerk angewählt (vorzugsweise B, C oder D). Mittels eines Dienstprogramms (z.B. POWER) sind die Funktionen Schreiben und Lesen zu überprüfen. Im Fehlerfall sollte zunächst der FDC wieder entfernt werden. Die Laufwerksauswahl und die Umschaltung der Steuerleitungen des Steuerregisters D3 ist leicht mit einem kleinen Testprogramm zu überprüfen (BASIC, PASCAL, ...). Dazu wird auf Adresse 0xc2 die gewünschte Bitbelegung ausgegeben. Durch ein Einlesen von Port 0xc1 werden D7 aktiviert und die Select-Signale zum Laufwerk weitergeschaltet. Damit sollte das Laufwerk aktiviert sein (Motor dreht sich, LED zeigt Aktivierung an). Alle weiteren Funktionen lassen sich statisch durch Anlegen der jeweiligen Pegel bzw. mittels eines einfachen TTL-Generators zur Lesedatensimulation prüfen. Somit ist z.B. die Datenstrecke zwischen D19 und Pin 23 (RDD) des Controllers sowie das Rasten der PLL kontrollierbar.

|

| Bild 2: Platinenlayout der Leiterseite der FDC-Leiterplatte |

|

| Bild 3: Platinenlayout der Bestückungsseite der FDC-Leiterplatte |

|

| Bild 4: Bestückungsplan der FD-Ansteuerplatine |

4 Anschluss von 8-Zoll Laufwerken

5 Software

Bildschirm:

16 Zeilen mit je 64 Zeichen und mit 16 Zwischenzeilen (Original-PC/M), dazu ist eine Statuszeile mit Angaben über Laufwerk, User, freie Speicherkapazität, maximale Speicherkapazität, Laufwerkstyp und Systemversion möglich

24 Zeilen mit je 80 Zeichen (Adresse 0xf800, Bit 7 = H : Cursor Ein)

Tastatur:

Original PC/M-Tastatur

K 7659

K 7672 über IFSS

S 3004 als Tastatur

Drucker:

SIO-Drucker SD 1152

K 6313/14 oder EPSON usw. über V.24

S 3004 als Drucker

Floppy:

Vier FD-Laufwerke unterschiedlicher Typen in mehreren Formaten (u.a. 148, 200, 308, 400, 624, 780, 800 KByte)

RAM-Floppy

6 FDC-PLL-Abgleich

V. Lühne (redaktionell gekürzt)

7 Zusätze und Erfahrungen

Dipl.-Ing.(FH) St. Linz

7.1 Schaltungsanalyse

7.2 Änderungen

auftrennen:

D1:4 zu D2:5 (IORQ) an D2, B-Seite

D5:2 zu D4:11 (RD) an D4, L-Seite

D5:1 zu D8:2 (/RD) an D8, L-Seite

D5:3 zu D8:3 (/WR) an D8, L-Seite

D5:4 zu D13:5 (WR) an D13, L-Seite

D6:8 zu D7:9 (0xc0..0xc3) an D7, L-Seite

D7:9 zu D8:4 und D4:9 (0xc0..0xc3) an [B]D7, B-Seite

verbinden:

D6:8 zu D8:4 (0xc0..0xc3)

neu:

D5:4 zu D13:12 (WR)

D5:2 zu D13:1 (RD)

D1:4 zu D13:13 und D13:2 und D14:10 (IORQ)

D13:11 zu D5:9 und D13:5 (IOWR)

D13:3 zu D5:11 und D4:11 (IORD)

D5:8 zu D8:3 (/IOWR)

D5:10 zu D8:2 (/IORD)

D6:8 zu D5:13 (~((0xc0 & 0xc1) | ~M1))

D5:12 zu D14:9

D14:8 zu D7:9

7.3 Stückliste

| Bez. | Typ | Wert | Beschreibung / Verweis |

| D1 | Schaltkreis | DL 004 D SN 74LS04 N K(M) 555 LN 1 |

6 Inverter, wie D5, D11, D17 |

| D2 | – " – | DL 030 D SN 74LS30 N K(M) 555 LA 2 |

1 NAND Gatter mit je 8 Eingängen |

| D3 | – " – | DS 8282 D I 8282 K(M) 580 IR 82 |

8 Bit Bustreiber und Speicher, invertierend, 3-State Ausgänge |

| D4 | – " – | DS 8286 D I 8286 K(M) 580 WA 86 |

bidirektionaler 8 Bit Bustreiber, nicht invertierend, 3-State Ausgänge |

| D5 | – " – | wie D1 | |

| D6 | – " – | DL 000 D SN 74LS00 N K(M) 555 LA 3 |

4 NAND Gatter mit je 2 Eingängen, wie D9, D14, D21, D28 |

| D7 | – " – | DL 123 D SN 74LS123 N K(M) 555 AG 3 |

2 monostabile Multivibratoren |

| D8 | – " – | U 8272-04 µP 765 I 8272 |

Steuerschaltkreis für Floppy-Disk Laufwerke (besser ist -08 für 8 MHz) |

| D9 | – " – | wie D6 | |

| D10 | – " – | DL 074 D SN 74LS74 N K(M) 555 TM 2 |

2 D-Flip-Flop, positiv flankengetriggert, wie D18, D23 |

| D11 | – " – | wie D1 | |

| D12 | – " – | DL 251 D SN 74LS251 N K(M) 555 KP 15 |

8 auf 1 Multiplexer, 3-State Ausgänge |

| D13 | – " – | DL 008 D SN 74LS08 N K(M) 555 LI 1 |

4 NAND Gatter mit je 2 Eingängen |

| D14 | – " – | wie D6 | |

| D15 | – " – | DL 121 D SN 74LS121 N K(M) 555 AG 1 |

bipolarer monostabiler Multivibrator mit Schmitt Trigger Eingängen, wie D19 |

| D16 | – " – | DL 193 D SN 74LN193 N K(M) 555 IE 7 |

4 Bit Vor-/Rückwärts-Zähler mit CLEAR |

| D17 | – " – | wie D1 | |

| D18 | – " – | wie D10 | |

| D19 | – " – | wie D14 | |

| D20 | – " – | D 150 D (D 251 D) SN 7450 N K(M) 155 LR 1 SN 74H51 N K(M) 131 LR 11 |

2 AND-NOR Gatter mit je 2x2 Eingängen, 1 Gatter erweiterbar |

| D21 | – " – | wie D6 | |

| D22 | – " – | DL 014 D SN 74LS14 N K(M) 555 TL 2 |

6 invertierende Treiber mit offenen Kollektoren (15 V), wie D25 |

| D23 | – " – | wie D6 | |

| D24 | – " – | DL 2632 D Am 26LS32 PC |

4facher Leitungsempfänger für Differenzsignale (V.11, RS-422A, RS-423A) |

| D25 | – " – | wie D22 | |

| D26 | – " – | DL 038 D SN 74LS38 N K(M) 555 LA 13 |

4 NAND Leistungsgatter mit je 2 Eingängen, offene Kollektorausgänge (5 V), wie D27, D29, D30 |

| D27 | – " – | wie D26 | |

| D28 | – " – | wie D6 | |

| D29 | – " – | wie D26 | |

| D30 | – " – | wie D26 | |

| A1 | Operations- verstärker |

B 082 Dm TL 082 |

BIFET-OPV CMR = 80-96 dB, SVR = 80-100 dB, SR = 13 V/µs |

| VT1 | Transistor | SC 307 D BC 307 |

Si-PNP-Planar, Uceo = -45 V, Ico = -100 mA, Ptot = 250 mW, h21 = 112-280 (bei -6 V, 2 mA, 1 kHz) |

| VD2 | Diode | SAY 30 andere: ??? |

Si-Planar, Ur = 25 V, If = 30 mA, Uf < 0,81 V |

| VD3 | – " – | SAL 41 andere: ??? |

Si-Mehrfachdiode, Ur = 15 V, If = 20 mA, Uf < 1,7 V, wie VD4 |

| VD4 | – " – | wie VD3 | |

| Q1 | Schwingquarz | 8 MHz (4 MHz) | |

| C1 | Elyt.-Kond. | 10 µF / 10 V | stehend, wie C2, C17 |

| C2 | – " – | wie C1 | |

| C3 | – " – | 22 µF / 10 V | stehend |

| C4 | Keramikkond. | 10 nF / 63 V | |

| C5 | – " – | 15 pF / 63 V | |

| C6 | – " – | 33 pF / 63 V | |

| C7 | – " – | 22 nF / 63 V | |

| C8 | – " – | 1 nF / 63 V | |

| C9 | – " – | 100 nF / 63 V | wie C10, C16 |

| C10 | – " – | wie C9 | |

| C11 | – " – | 47 nF / 63 V | |

| C12 | – " – | 470 pF / 63 V | |

| C13 | – " – | wie C11 | |

| C14 | Elyt.-Kond. | 100 µF / 10 V | liegend, wie C15 |

| C15 | – " – | wie C14 | |

| C16 | Keramikkond. | wie C9 | |

| C17 | Elyt.-Kond. | wie C1 | |

| C18 | Keramikkond. | 100 pF / 63 V | |

| Stütz-C | – " – | 33 nF / 63 V | 16 mal, 22 nF auch möglich |

| R1 | Einst.-Regl. | 470 | stehend, klein |

| R2 | Widerstand | 320 | Dickschicht, ¼ W |

| R3 | – " – | 270 | – " – |

| R4 | – " – | 68 | – " – |

| R5 | – " – | 33 | – " – |

| R6 | – " – | 47 k | – " – |

| R7 | – " – | 680 | – " –, wie R28, R29, R30, R34, R35, R36 |

| R8 | – " – | 510 | – " –, wie R10 |

| R9 | – " – | 100 | – " –, wie R24 |

| R10 | – " – | wie R8 | |

| R11 | – " – | 620 | – " – |

| R12 | – " – | 39 k | – " – |

| R13 | – " – | 12 k | – " –, wie R17 |

| R14 | – " – | 150 | – " –, wie R18 |

| R15 | – " – | 1,8 k | – " –, wie R16 |

| R16 | – " – | wie R15 | |

| R17 | – " – | wie R13 | |

| R18 | – " – | wie R14 | |

| R19 | – " – | 220 | – " –, wie R20 |

| R20 | – " – | wie R19 | |

| R21 | – " – | 22 k | – " – |

| R22 | – " – | 27 k | – " – |

| R23 | – " – | 120 | – " – |

| R24 | – " – | wie R9 | |

| R25 | – " – | 470 | – " –, wie R26, R27, R31, R32, R33 |

| R26 | – " – | wie R25 | |

| R27 | – " – | wie R25 | |

| R28 | – " – | wie R7 | |

| R29 | – " – | wie R7 | |

| R30 | – " – | wie R7 | |

| R31 | – " – | wie R25 | |

| R32 | – " – | wie R25 | |

| R33 | – " – | wie R25 | |

| R34 | – " – | wie R7 | |

| R35 | – " – | wie R7 | |

| R36 | – " – | wie R7 | |

| R37 | – " – | 1 k | – " – |

| R38 | – " – | 3,3 k | – " – |

| R39 | – " – | 330 k | – " – |

| R40 | – " – | 750 | – " –, wie R41 |

| R41 | – " – | wie R40 | |

| R42 | – " – | 820 | – " – |

| L1 | UKW Drossel | 10 µH / 1,6 A | wie L2 |

| L2 | – " – | wie L1 | |

| X1 | Steckerleiste | 304-58 TGL 29331/03 | 58-polig, abgewinkelt, indirekt für LP, RM 2,51 mm |

| X2 | Buchsenleiste | ###-26 TGL 29331/## | 26-polig, abgewinkelt, indirekt für LP, RM 2,51 mm |

| X3 | Wickelstifte | 6 mal (X3:1 bis X3:6), Vierkantstifte |

hochauflösende Abbildungen

Scans vom Original in niedriger Qualität

PCM_FDC_FA021990_LQ.pdf

PCM_FDC_FA021990_LQ.pdf

Teil FDC: FA-2/1990 S.63-66, 3.US, FA-9/1990 S.441

pdf, 569.6K, 11/19/05, 1264 downloads

PC/M Bauanleitung FA-102/1990 S.63-66, 3.US, FA-9/1990 S.441

Scans vom Original in hoher Qualität

PCM_FDC_FA021990_1_HQ.pdf

PCM_FDC_FA021990_1_HQ.pdf

Teil FDC I: FA-2/1990 S.63-64

pdf, 2.7M, 11/19/05, 1067 downloads

PC/M Bauanleitung Teil FDC: FA-2/1990 S.63-64

PCM_FDC_FA021990_2_HQ.pdf

PCM_FDC_FA021990_2_HQ.pdf

Teil FDC II: FA-2/1990 S.66-66

pdf, 2.7M, 11/19/05, 1060 downloads

PC/M Bauanleitung Teil FDC: FA-2/1990 S.65-66

PCM_FDC_FA021990_3_HQ.pdf

PCM_FDC_FA021990_3_HQ.pdf

Teil FDC III: FA-2/1990 3.US, FA-9/1990 S.441

pdf, 2.7M, 11/19/05, 1014 downloads

PC/M Bauanleitung Teil FDC: FA-2/1990 3.US, FA-9/1990 S.441

| Autor: | Stephan Linz |

| Revision: | 2021/01/14 - 00:07 - © Li-Pro.Net |